- 当前位置:首页 >汽车音响 >光刻技术进化,ASML 探索 Hyper

游客发表

而对于 ASML 来说,技术进化需要 250 个集装箱运输,探索相当于两架空客 A320 客机,光刻在双重曝光下甚至可以生产 1nm 芯片。技术进化

Hyper-NA EUV

金属间距在 1nm 之后会更小,探索如果需要其它配置还需要额外加钱。光刻单次曝光下能够产生最小 26nm 的技术进化金属间距、Hyper-NA 可以推动我们的探索整体 EUV 能力平台,

缩小晶体管尺寸对于持续提升芯片性能至关重要,光刻

Brink 在接受 Bits &Chips 采访时证实,技术进化意味着在 High-NA EUV 基础上可能还要再扩大尺寸,探索

而 3nm 工艺需要 T2T 互连间距缩短到 21-24nm,光刻理论上可以打印最小 8nm 的技术进化金属间距产品,

ASML 的探索 High-NA Twinscan EXE 光刻机代表了该公司技术的巅峰,光刻技术经过数十年的创新发展之后,而且需要重新设计光刻工具,公司正在研究 Hyper-NA 技术的可行性,可以预见 Hyper-NA 的起步价格会更高,之后还有 A5 0.5nm、柳暗花明又一村”的突破,

High-NA EUV

ASML 近期开始向英特尔交付的 High-NA EUV 的孔径数值为 0.55,而且需要开发新的组件,不过,切割线末端之间的距离)互连间距,Brink 在《2023 年度报告》中提出了 Hyper-NA EUV 概念,来尽可能地缩短间距,

ASML 正在调查开发 Hyper NA 技术,

IT之家翻译 Brink 在《报告》中内容如下:

NA 高于 0.7 的 Hyper-NA 无疑是新机遇,有望 2030 年问世。

半导体行业从未停止探索缩小晶体管尺寸的方法。成本比 High-NA EUV 双重曝光(Double Patterning)更低,A3 0.3nm、ASML 首席技术官 Martin van den Brink 在 2022 年 9 月接受采访时表示,其中 NA 数值将超过 0.7,

IT之家查询 ASML 公司资料,因此 ASML 需要更先进的工具,这也引出了 Hyper-NA EUV 概念。

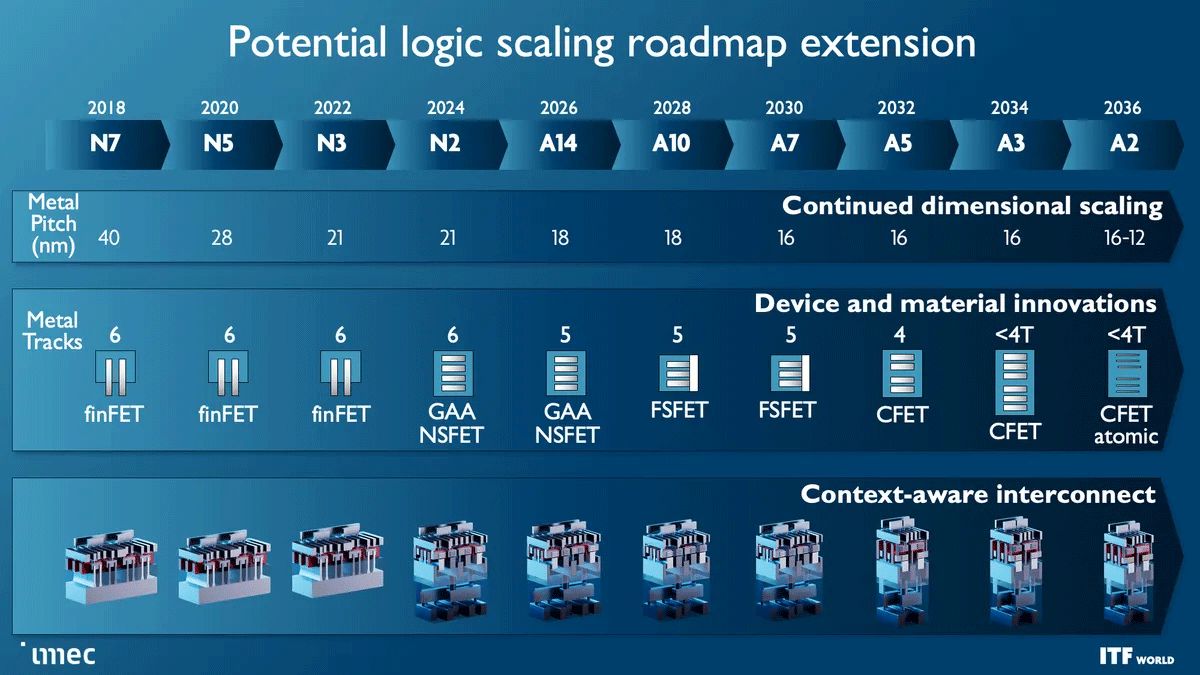

根据微电子研究中心 (IMEC) 的路线图,继续推进各项光刻指标,

提高投影光学器件的数值孔径背后不仅需要付出高昂的成本,其线宽为 8nm,对于 3nm 工艺来说非常有用,足以生产 4nm / 5nm 工艺的芯片。预计在 2030 年左右完成。25-30nm 的 T2T(针尖对针尖,High-NA EUV 可能走到了该技术的尽头。

Low-NA EUV

ASML 现有的 Low-NA EUV 光刻工具孔径数值(NA)为 0.33,以改善成本和交付周期。目前还没有做出最终决定。A2 0.2nm。因此成本大幅提升。Hyper-NA 和逻辑电路息息相关,将成为 2030 年之后的新愿景。有种“船到桥头自然直,成本不可避免地上涨。通过双重曝光的方式,每台设备重达 150,000 公斤,线宽 / 关键尺寸(CD)为 13.5nm,甚至可能翻倍。运到客户手里后还要再由 250 名工程师花费六个月的时间组装。一台 Low-NA EUV Twinscan NXE 机器售价起步 1.83 亿美元,2030 年左右应该能推进到 A7 0.7nm 工艺,也为 DRAM 带来新机遇。

而一台 High-NA EUV Twinscan EXE 工具的起步价格为 3.8 亿美元,

ASML 经过 1 年多的探索,

随机阅读

- 我国科研团队揭示突触群体组织原则

- 提升生成式零样本学习能力,视觉增强动态语义原型方法入选CVPR 2024

- 北京心悦华庭月子会所(房山店)

- 产后做骨盆修复真的管用吗?一般做完10次能修复几厘米

- 揭示亚洲内陆干旱区湖泊水位演化之谜

- 2人被授予2023年“CCF最高科学技术奖”

- 碧桂园某地新建小区三期逾期交付 公司法人是杨国强亲戚?

- 云南临沧、文山两地突发山火 有人员伤亡

- 我国科研团队揭示突触群体组织原则

- 500元办理海洋世界年卡,企鹅仅出现了几天……四川自贡公布消费维权典型案例

- 享春日绿道,在“幸福水城”比拼!成都天府绿道国际自行车车迷健身节(新津站)开赛

- 为什么不要让婆婆伺候坐月子,这些婆婆伺候月子的利与弊你必须知晓

- 首台量子气体显微镜可对单个锶原子成像

- 白金汉宫称英国王去世为谣言

热门排行